In December 2019, TSMC announced an average yield of approximately 80%, with a peak yield per wafer of over 90% for their 5 nm test chips with a die size of 17.92 mm 2. In October 2019, TSMC reportedly started sampling 5 nm A14 processors for Apple. įor their 5 nm process, Samsung started process defect mitigation by automated check and fix, due to occurrence of stochastic (random) defects in the metal and via layers. For the expected 28 nm minimum metal pitch, SALELE is the proposed best patterning method.

The N5 process can use EUVL on up to 14 layers, compared to only 5 or 4 layers in N6 and N7++.

MINIMUM FEATURE SIZE TRANSISTOR DEFINITION FULL

In April 2019, TSMC announced that their 5 nm process (CLN5FF, N5) had begun risk production, and that full chip design specifications were now available to potential customers.

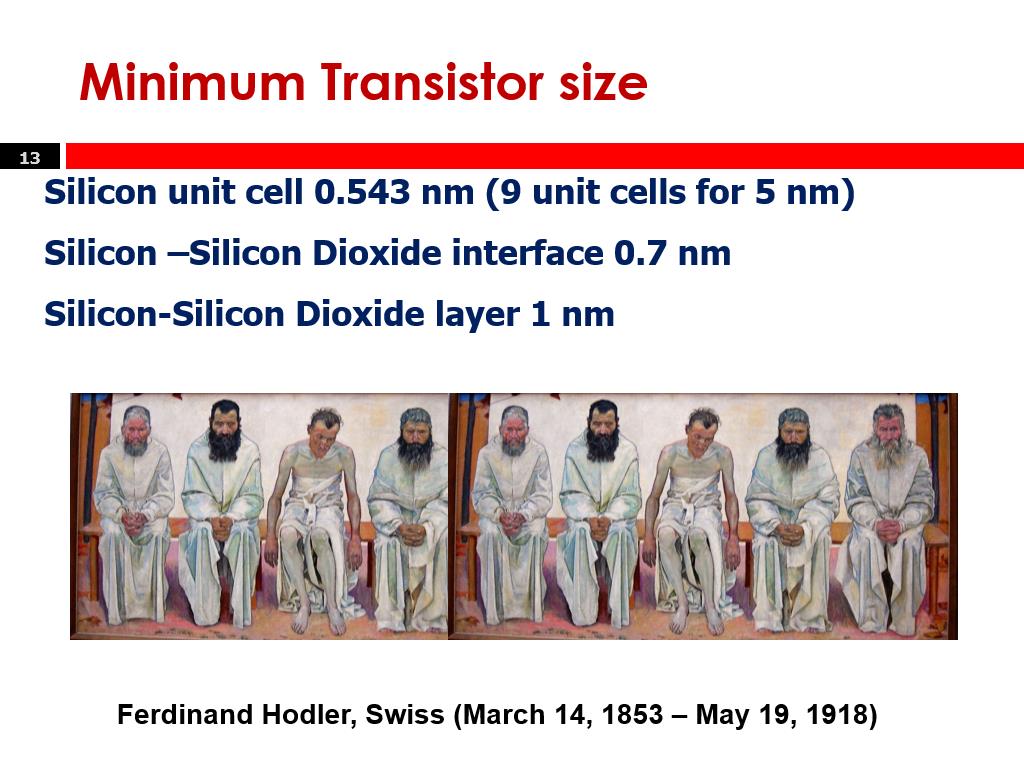

In April 2019, Samsung Electronics announced they had been offering their 5 nm process (5LPE) tools to their customers since 2018 Q4. IBM's chip measured 50 mm 2 and had 600 million transistors per mm 2, for a total of 30 billion transistors (1667 nm 2 per transistor or 41 nm transistor spacing). The GAAFET transistors used had 3 nanosheets stacked on top of each other, covered in their entirety by the same gate, just like FinFETs usually have several physical fins side by side that are electrically a single unit and are covered in their entirety by the same gate. In 2017, IBM revealed that it had created 5 nm silicon chips, using silicon nanosheets in a gate-all-around configuration (GAAFET), a break from the usual FinFET design. In 2015, Intel described a lateral nanowire (or gate-all-around) FET concept for the 5 nm node. The fabricated test chips are not fully functional devices but rather are to evaluate patterning of interconnect layers. In 2015, IMEC and Cadence had fabricated 5 nm test chips. In 2003, a Japanese research team at NEC, led by Hitoshi Wakabayashi and Shigeharu Yamagami, fabricated the first 5 nm MOSFET. In 2002, an IBM research team including Bruce Doris, Omer Dokumaci, Meikei Ieong and Anda Mocuta fabricated a 6-nanometre silicon-on-insulator (SOI) MOSFET. Single-transistor devices below 7 nm were first demonstrated by researchers in the early 2000s. Quantum tunnelling effects through the gate oxide layer on 7 nm and 5 nm transistors became increasingly difficult to manage using existing semiconductor processes. a higher degree of miniaturization), increased speed and reduced power consumption compared to the previous 7 nm process.

However, in real world commercial practice, "5 nm" is used primarily as a marketing term by individual microchip manufacturers to refer to a new, improved generation of silicon semiconductor chips in terms of increased transistor density (i.e.

MINIMUM FEATURE SIZE TRANSISTOR DEFINITION UPDATE

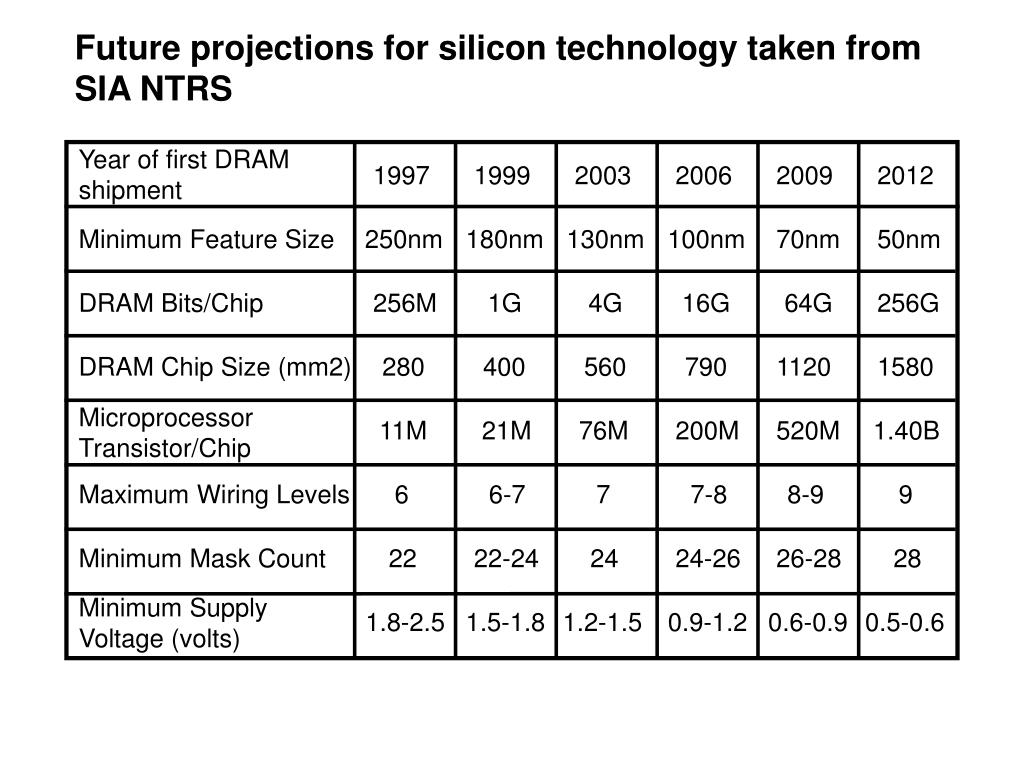

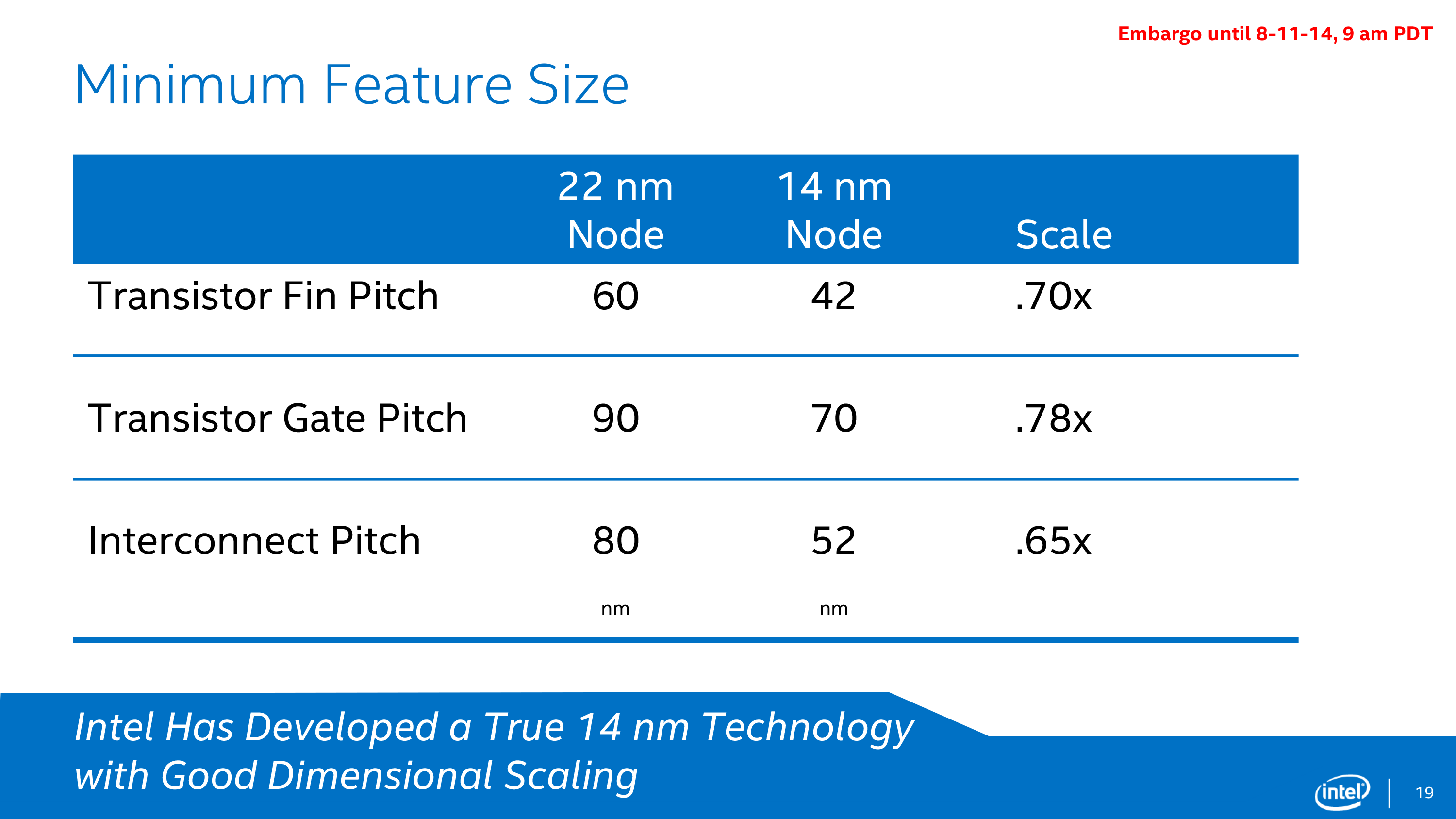

According to the projections contained in the 2021 update of the International Roadmap for Devices and Systems published by IEEE Standards Association Industry Connection, a "5 nm node is expected to have a contacted gate pitch of 51 nanometers and a tightest metal pitch of 30 nanometers". The term "5 nm" has no relation to any actual physical feature (such as gate length, metal pitch or gate pitch) of the transistors being 5 nanometers in size. In 2020, Samsung and TSMC entered volume production of 5 nm chips, manufactured for companies including Apple, Marvell, Huawei and Qualcomm. In semiconductor manufacturing, the International Roadmap for Devices and Systems defines the 5 nm process as the MOSFET technology node following the 7 nm node.

0 kommentar(er)

0 kommentar(er)